Dünner Kirchweg 77 32257 Bünde Germany www.trenz-electronic.de

#### 2001-November-6

### Introduction

This tutorial was created to give the interested engineer a quick hands on experience on the Xilinx' *WebPACK ISE* software suite.

The tutorial provides only a very brief overview of FPGA design methodology without going into too much detail. After completing this tutorial and the first own design steps, it is highly recommended to proceed with further readings, e.g. the various application notes and online manuals.

While concentrating on the basic steps and methods, it is also the goal of this tutorial to cover the complete development cycle. Beginning with design entry, through simulation, synthesis

# Spartan-II Development System

### Tutorial: First Steps with WebPACK ISE

and implementation up to the download to physical hardware all covered in a single, consistent project.

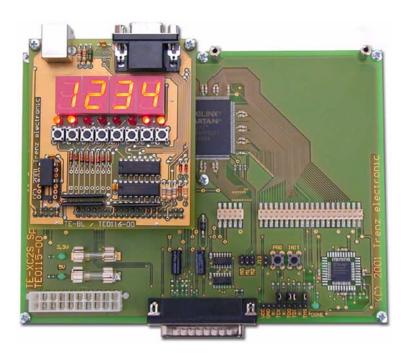

To achieve both of these goals, we decided to design a very simple hexadecimal counter which is implemented on our *TE-XC2S* Spartan-II Development System. All steps required to complete this design are covered by this tutorial. There are no hidden steps or imported and half-completed files. While this limits the possible size of the project (without exceeding a certain time frame) we feel that there is still no better way of learning something than from own experience.

Happy developing!

Figure 1: Spartan-II Development System

## **Download and Installation**

In case you did not receive the Xilinx *WebPACK ISE* software on CD-ROM, you may download the latest revision from <u>www.xilinx.com</u>. From the home page follow the links to

Buy Online WebPACK

If you do not have a Xilinx account yet, you will need to register with Xilinx and create and account. To do so, follow the link to

Register for WebPACK ISE

In case you already registered with Xilinx, follow the link to

Single File Download

This will lead you to the following screen:

Click Design Configurations, FPGA Design, Select Configuration...

| Getting Started       | 1           |                      |

|-----------------------|-------------|----------------------|

| Design Configurations | CPLD Design |                      |

| Individual Modules    | FPGA Design | Select Configuration |

| Latest Updates        |             |                      |

... and the following box appears:

Clicking the Download button, pops up the Download Manager window. The software is divided into several modules, which may be downloaded and installed separately.

| 🖲 Download WebP   | ACK - Micros 💶 🔲 🗙     |

|-------------------|------------------------|

| <b>S</b> XILINX   | Download Manager       |

| C. AILINA         |                        |

| Instructions Y    | ou have chosen the     |

| following module  | s. Please click on the |

| links below to sa | ve / install the       |

| WebPACK ISE       | Software.              |

| Modules Select    | ed                     |

| Design Entry      |                        |

| Spartan Fitter    |                        |

| Virtex Fitter     |                        |

| FPGA Programm     | <u>her</u>             |

| MXE Simulator     |                        |

| MXE VHDL FP       | GA Library             |

| MXE Verilog FP    | GA Library             |

| StateCAD          |                        |

| HDL Bencher       |                        |

|                   |                        |

The following tutorial assumes, that you download and install the following modules:

- Design Entry

- Spartan Fitter

- FPGA Programmer

- MXE Simulator

- MXE VHDL FPGA Library

- StateCAD

In Version 3.3WP8.x these files sum up to approximately 92MB of transfer volume and about 350MB of disk space after installing.

Optionally, you may download the following optional files, which sum up to another 40MB:

- Virtex Fitter

- MXE Verilog FPGA Library

- HDL Bencher

## **Creating a design**

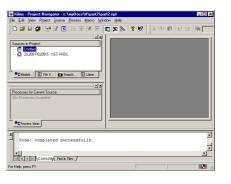

After launching the *WebPACK Project Navigator* for the first time, it comes up with an empty screen, divided into several panes. The *Source* window lists all sources being included in a project. The *Process* window lists the possible actions for a selected source. The *Edit* window is used to display and modify HDL sources. The *Transcript* window shows a log of the most recent shell operations.

Before going further, we need to create a new project.

| Xilinx - Project Navigator - c:\myDocs\tt\part2\part2.npl |                                               |  |  |  |

|-----------------------------------------------------------|-----------------------------------------------|--|--|--|

| <u>File</u> <u>E</u> dit <u>V</u> iew Project             | <u>Source Process Macro Window H</u> elp      |  |  |  |

| Ne <u>w</u> Project                                       | <b></b> 5   1   1   1   1   1   1   1   1   1 |  |  |  |

| Open P <u>r</u> oject                                     |                                               |  |  |  |

| Open Exa <u>m</u> ple                                     |                                               |  |  |  |

| Close Projec <u>t</u>                                     |                                               |  |  |  |

| Sa <u>v</u> e Project As                                  |                                               |  |  |  |

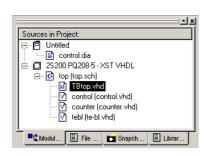

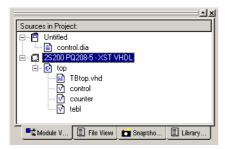

A dialog pops up to specify the project's name and location. Furthermore the target family and device as well as the synthesis tool need to be chosen. To target the *TE-XC2S* board, we need to specify *Spartan2* as the device family and *2S200PQ208-5* as the device. Our synthesis tool is *XST VHDL*.

| ew Project                          |             |                                                  |

|-------------------------------------|-------------|--------------------------------------------------|

| Project name:                       | Project Loc | ation:                                           |

| part2                               | c:\myDocs   | <pre>\tt\part2</pre>                             |

| Project Doujee Options:             |             |                                                  |

| Project Device Options:<br>Property | Name        | Value                                            |

| Property                            | Name        |                                                  |

|                                     | r Name      | Value           Spartan2           2S200 PQ208-5 |

After closing the dialog, an empty project will be created in the project location specified above:

## **Design entry**

## **Adding existing Source Files**

We start our project by adding an existing VHDL module to it. Copy the file from the CD-ROM into your project location, before proceeding. You may use the Windows Explorer to do so.

| Xilinx - Project Navigator - c:\myDocs\tt\part2\part2.npl |              |                               |         |               |                |              |            |

|-----------------------------------------------------------|--------------|-------------------------------|---------|---------------|----------------|--------------|------------|

| <u>F</u> ile <u>E</u> dit <u>V</u> iew                    | Project      | <u>S</u> ource                | Process | <u>M</u> acro | <u>₩</u> indow | <u>H</u> elp |            |

| 🗏 D 🚅 🗔 🕻                                                 | <u>N</u> ew  | Source                        |         |               |                | <b>5</b> 8.  | <b>?</b> № |

|                                                           | Add          | Add Source In                 |         |               | rt             | <b>m</b> 70  |            |

|                                                           | Add          | Add Copy of Source Shift+Inse |         |               | t+Insert       |              |            |

| Sources in Project                                        | <u>D</u> ele | Delete Implementation Data    |         |               |                |              |            |

The file *TE-BL.vhd* comes with your *TE-XC2S* Development System and contains commonly used code to interface with the *Buttons & Lights* Expansion Board.

| Add Existing        | Sources                                |          |     | ? ×             |

|---------------------|----------------------------------------|----------|-----|-----------------|

| <u>S</u> uchen in:  | 🔄 part2                                | •        | * 🖻 | •               |

| te-bl.vhd           |                                        |          |     |                 |

|                     |                                        |          |     |                 |

|                     |                                        |          |     |                 |

|                     |                                        |          |     |                 |

|                     |                                        |          |     |                 |

| Datei <u>n</u> ame: | te-bl.vhd                              |          |     | Ö <u>f</u> fnen |

| Datei <u>t</u> yp:  | Sources (*.txt;*.sch;*.vhd;*.vhd;*.vhd | ;*.dia;) | J [ | Abbrechen       |

A *.vhd* suffix is ambiguous, as VHDL files may contain packages, modules, or test benches. Our file contains a VHDL entity or *module*.

| Choose Source Type                                                     | ×            |

|------------------------------------------------------------------------|--------------|

| te-bl.vhd is which source type?<br>The suffix is ambiguous as to type. |              |

| VHDL Module<br>VHDL Package<br>VHDL Test Bench                         | OK<br>Cancel |

The file is added to the source window. The name of the VHDL entity, *tebl*, is displayed, followed by the name of the source file, *te-bl.vhd*, in parentheses.

| Sources in Project:                 |

|-------------------------------------|

| 👘 🖻 Untitled                        |

|                                     |

| tebl (te-bl.vhd)                    |

|                                     |

| ■L Module E File V La Snapsh Librar |

| 📑 Module 📋 File V 💼 Snapsh 🗐 Librar |

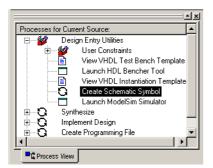

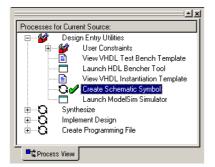

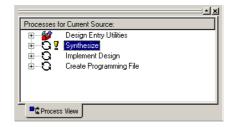

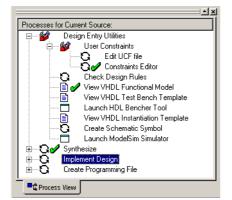

In the process window, we double click *Create Schematic Symbol*, as we want to use the entity tebl in a schematic diagram later on.

| Processes for Current Source:                                              |  |  |  |  |

|----------------------------------------------------------------------------|--|--|--|--|

| 🖃 🗝 💕 Design Entry Utilities                                               |  |  |  |  |

| 😟 🤡 User Constraints                                                       |  |  |  |  |

| View VHDL Test Bench Template                                              |  |  |  |  |

| Launch HDL Bencher Tool                                                    |  |  |  |  |

| View VHDL Instantiation Template                                           |  |  |  |  |

|                                                                            |  |  |  |  |

| Launch ModelSim Simulator                                                  |  |  |  |  |

| 🗄 🗠 🖸 Synthesize                                                           |  |  |  |  |

| Synthesize     Synthesize     Implement Design     Create Programming File |  |  |  |  |

| 🗄 🖳 🛱 Create Programming File                                              |  |  |  |  |

| -                                                                          |  |  |  |  |

| Process View                                                               |  |  |  |  |

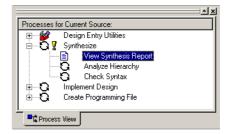

Successful generation of the schematic symbol is indicated by a green check mark.

| Processes for Current Source:          |

|----------------------------------------|

| 🖃 🗝 💅 🛛 Design Entry Utilities         |

| 🕀 🚽 User Constraints                   |

| 📄 🛛 View VHDL Test Bench Template      |

| Launch HDL Bencher Tool                |

| 📄 🛛 📄 View VHDL Instantiation Template |

|                                        |

| Launch ModelSim Simulator              |

| 🗄 🗠 🖸 Synthesize                       |

| 🗄 🕀 Implement Design                   |

| 🗄 🗠 😋 Create Programming File          |

|                                        |

| Process View                           |

### Using the HDL Editor

Next, we create a new VHDL file and add it to the project.

| Nilinx - Project Navigator - c:\myDocs\tt\part2\part2.npl |                                                |                            |         |               |                       |              |     |

|-----------------------------------------------------------|------------------------------------------------|----------------------------|---------|---------------|-----------------------|--------------|-----|

| <u>F</u> ile <u>E</u> dit ⊻iew                            | P <u>r</u> oject ,                             | <u>S</u> ource             | Process | <u>M</u> acro | $\underline{W} indow$ | <u>H</u> elp |     |

|                                                           | New Source<br>Add Source<br>Add Copy of Source |                            |         | Inse<br>Shifi | rt<br>t+Insert        | <b>a</b> 54  | १ № |

| Sources in Proje                                          | Delete                                         | Delete Implementation Data |         |               |                       |              |     |

A dialog box appears, to specify the type of source to create, the file name and location. As we want to create another VHDL entity, we chose VHDL Module.

| New                                                                                                 | ×                                                        |

|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| New User Document Schematic VHDL Maclule VHDL Test Bench VHDL Test Bench VhdL Library State Diagram | File Name:<br>counter<br>Logation:<br>c:\mydocs\tt\part2 |

| < Zurück W                                                                                          | eiter > Abbrechen Hilfe                                  |

Next, an assistant pops up, querying information required, to create a skeleton for our VHDL entity declaration and architecture body. We need to add port name, and direction for every port. For buses, we need to specify the MSB and LSB as well.

| Define VHDL Source     |                        |         |       | ×        |

|------------------------|------------------------|---------|-------|----------|

| _                      |                        |         |       | _        |

| Entity Name cour       | nter                   |         |       |          |

| Architecture Name beha | avioral                |         |       |          |

| Port Name              | Direction              | MSB     | LSB   | <b> </b> |

| clk                    | in                     |         |       |          |

| rst                    | in                     |         |       |          |

| en                     | in                     |         |       |          |

| count                  | out                    | 15      | 0 🚖   | 1        |

|                        | in                     |         |       |          |

|                        | in                     |         |       | 4        |

|                        | in                     |         |       |          |

|                        | in                     |         |       | 4        |

|                        | in                     |         |       | 4        |

|                        | in                     |         |       | -        |

|                        | in<br>in               |         |       | -        |

|                        |                        |         |       |          |

|                        |                        |         |       |          |

| < <u>Z</u>             | urück <u>W</u> eiter > | Abbreck | nen H | lilfe    |

Before creating the skeleton source, a summary window is displayed.

| Project Navigat<br>following specif |                     | te a new sk       | eleton source        | e with the |       |

|-------------------------------------|---------------------|-------------------|----------------------|------------|-------|

| Source Type: V                      |                     | le                |                      |            |       |

| Source Name: o                      |                     |                   |                      |            |       |

| Entity Name: co<br>Architecture Nar |                     | oral              |                      |            |       |

| Port Definitions:                   |                     |                   |                      |            |       |

| -                                   | clk                 | scalar            |                      | in         |       |

|                                     | rst                 | scalar            |                      | in         |       |

|                                     | en<br>count         | scalar<br>vector: | 15:0                 | in<br>out  |       |

|                                     | Count               | vector.           | 10.0                 | out        |       |

|                                     |                     |                   |                      |            |       |

|                                     |                     |                   |                      |            |       |

|                                     |                     |                   |                      |            |       |

|                                     |                     |                   |                      |            |       |

|                                     |                     |                   |                      |            |       |

|                                     |                     |                   |                      |            |       |

| Source Direct                       | our c'imi           | docs\tt\pa        | +2                   |            |       |

| Source Direct                       | ory: c:\my          | docs\tt\pa        | rt2                  |            |       |

| Source Direct                       | ory: c:\my          | docs\tt\pa        | ıt2                  |            |       |

| Source Direct                       | tory: c:\my<br>< Zu |                   | rt2<br>ertig stellen | Abbrechen  | Hilfe |

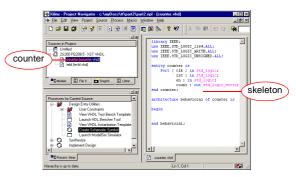

And finally, the source file is created and added to the project.

We complete the architecture body by adding the following lines to it:

```

architecture behavioral of counter is

signal counter: STD_LOGIC_VECTOR(count'range);

signal div: STD_LOGIC_VECTOR(16 downto 0);

signal div:

signal divl, en2: STD_LOGIC;

begin

process(clk, rst)

begin

if rst= 'l' then

div <= (others=> '0');

div1<= '0';

en2 <= '0';

elsif rising edge(clk) then

div <= div + 1;

divl<= div(div'left);

en2 <= div(div'left) and not(div1);</pre>

end if:

end process;

process(clk, rst)

begin

if rst= 'l' then

counter<= x''0000'';

elsif rising_edge(clk) then

if en= 'l' and en2= 'l' then

counter<= counter + 1;</pre>

end if:

end if:

end process;

count<= counter;

end behavioral;

```

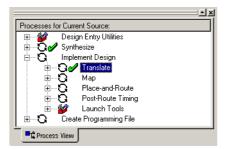

And like before, create a schematic symbol. We need to select our newly created source first...

... double click Create Schematic Symbol...

... and a green check mark indicates successful generation of the symbol.

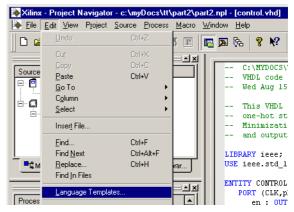

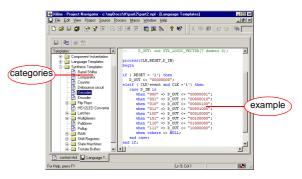

In case we have questions about VHDL, or need some inspiration, there are language templates.

The left pane sorts the templates by category, while the right pane displays the actual sample code.

Check out the language templates and get familiar with the editor! It behaves much like any other programming editor, so you shouldn't have a hard time doing so.

### Using the FSM Editor

Now we create a finite-state machine using the FSM Editor.

| <b>X</b>     | ilinx -      | Proje    | ct Navig    | ator - c:      | \myDocs | \tt\part      | 2\part2.r             | npl          |     |

|--------------|--------------|----------|-------------|----------------|---------|---------------|-----------------------|--------------|-----|

| <u>F</u> ile | <u>E</u> dit | ⊻iew     | Project     | <u>S</u> ource | Process | <u>M</u> acro | $\underline{W} indow$ | <u>H</u> elp |     |

| Шn           | <b>É</b>     | E ć      | <u>N</u> ew | Source         |         |               |                       | <b>N</b> R.  | 🤊 💦 |

|              | Add Source   |          | Inse        | rt             |         |               |                       |              |     |

|              |              |          | Add         | Copy of S      | ource   | Shif          | t+Insert              |              |     |

| So           | urces i      | in Proie |             |                |         |               |                       |              |     |

A dialog pops up, to query further information about the new source file. We chose *State Diagram* here.

| New<br>User Document<br>Schematic<br>VHDL Module<br>VHDL Package<br>VHDL Package | X                     |

|----------------------------------------------------------------------------------|-----------------------|

| Vhdl Library<br>State Diagram                                                    | control               |

|                                                                                  | c:\mydocs\tt\part2    |

|                                                                                  | Add to project        |

| < Zuriick 🔛                                                                      | eiter >AbbrechenHilfe |

Before creating the new diagram, a summary window is displayed.

| Project Navigator will create a new skeleton source with the<br>following specifications: Source Type: State Diagram Source Name: control |  |

|-------------------------------------------------------------------------------------------------------------------------------------------|--|

| Source Name: control                                                                                                                      |  |

| Course Directory, extendent/Ward2                                                                                                         |  |

| Course Directory extendent/Ward?                                                                                                          |  |

| Course Directory extendent/Ward2                                                                                                          |  |

| Course Directory estandee (Weed)                                                                                                          |  |

| Course Directory estander (West)                                                                                                          |  |

| Course Directory - claude - (Mar 42                                                                                                       |  |

|                                                                                                                                           |  |

| Source Directory: c:\mydocs\tt\part2                                                                                                      |  |

| <zurück abbrechen="" fertig="" hilfe<="" stellen="" td=""><td></td></zurück>                                                              |  |

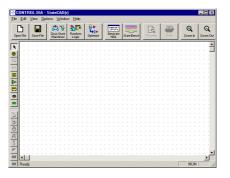

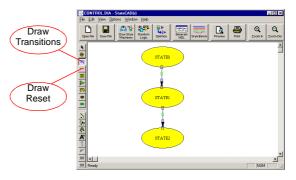

Next, the FSM Editor is launched, displaying an empty sheet.

We use the *Draw States* tool, to add a few states to our FSM.

|             | CONTROL.DIA - StateCAD(r)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                 |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

|             | Elle Edit View Options Window Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                 |

|             | Open File         Save File <t< td=""><td>Com In Zoom Dut</td></t<> | Com In Zoom Dut |

| Draw States | STATE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1               |

|             | 8 €<br>10 €<br>10 €<br>10 €<br>10 €                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                 |

|             | N<br>R<br>R<br>R<br>R<br>R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                 |

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                 |

|             | Ready                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | NUM             |

Next, we use the *Draw Transitions* tool, to connect our states.

We chose the *Draw Reset* tool, to add a reset to *State0*, and will be prompted for the type of reset. We select *asynchronous* here.

| StateCAL | )                           |                                 | ×   |

|----------|-----------------------------|---------------------------------|-----|

| ?        | Should this reset be asyncl | hronous (Yes) or synchronous (N | o)? |

|          |                             | <u>N</u> ein                    |     |

Now our machine looks like this:

In the following, we edit the state's properties. A double click on *State0* pops up the following dialog. We alter the state name and add an output.

| Edit State 🗙                                                                      |

|-----------------------------------------------------------------------------------|

| State Name: idle                                                                  |

| Outputs: Unassigned outputs are made inactive (i.e. q=0)                          |

| en<= '0';                                                                         |

| Output Wizard Create counters, muxes, etc. with the wizard.                       |

| Justify State Name         Justify Output           C Left C Center         Bight |

| OK Cancel Help                                                                    |

We do the same for State1...

| Edit State 🛛 🗙                                              |

|-------------------------------------------------------------|

| State <u>N</u> ame: run                                     |

| Outputs: Unassigned outputs are made inactive (i.e. q=0)    |

| en<= '1';                                                   |

| <b>_</b>                                                    |

| Output Wizard Create counters, muxes, etc. with the wizard. |

| Justify State Name<br>C Left © Center C Bight               |

| OK Cancel Help                                              |

... and State2.

| Edit State 🗙                                                |

|-------------------------------------------------------------|

| State Name: stop                                            |

| Outputs: Unassigned outputs are made inactive (i.e. q=0)    |

| en<= '0';                                                   |

| ×                                                           |

| Output Wizard Create counters, muxes, etc. with the wizard. |

| Justify State Name                                          |

| C Left C Center C Bight                                     |

| OK Cancel Help                                              |

Next, we need to set up the transitions. Double clicking on the transition from *idle* to *run* pops up the following dialog. We add a condition to this transition.

| Edit Condition 🗙                                                                                           |

|------------------------------------------------------------------------------------------------------------|

| Condition:                                                                                                 |

| pbrun= '1'                                                                                                 |

| <u>·</u>                                                                                                   |

| Outputs: Unassigned outputs are made inactive (i.e. q=0)                                                   |

|                                                                                                            |

|                                                                                                            |

| T                                                                                                          |

| Output Wizard To edit equations created with the wizard, place the cursor in the equation and click Output |

| Justify Condition Justify Output                                                                           |

| C Left Center C Bight C Left C Center C Bight                                                              |

| Mutually Exclusive Border                                                                                  |

| Priority 0 + 0K Cancel Help C Asynchronous                                                                 |

For the transition connecting *run* with *stop* we need to add a similar condition:

| Edit Condition 🔀                                                                                           |

|------------------------------------------------------------------------------------------------------------|

| Condition:                                                                                                 |

| pbstop= '1                                                                                                 |

| -                                                                                                          |

| Outputs: Unassigned outputs are made inactive (i.e. q=0)                                                   |

|                                                                                                            |

|                                                                                                            |

|                                                                                                            |

| Output Wizard To edit equations created with the wizard, place the cursor in the equation and click Output |

| Justify Condition                                                                                          |

| C Left ⊙ Center C Bight C Left ⊙ Center C Bight                                                            |

| Mutually Exclusive Border                                                                                  |

| Priority 0 👗 OK Cancel Help C Asynchronous                                                                 |

Our reset vector is already properly set up, but to be sure, we may open the according dialog as well:

| Edit Condition 🛛 🔀                                                                                         |

|------------------------------------------------------------------------------------------------------------|

| Condition:                                                                                                 |

| RESET                                                                                                      |

| -                                                                                                          |

| Outputs:                                                                                                   |

| <u>^</u>                                                                                                   |

|                                                                                                            |

| <u>_</u>                                                                                                   |

| Output Wizard To edit equations created with the wizard, place the cursor in the equation and click Output |

| Justify Condition Justify Output                                                                           |

| C Left 	Center C Bight C Left 	Center C Bight                                                              |

| Mutually Exclusive     Border     Mode     C Synchronous                                                   |

| OK Cancel Help © Asynchronous                                                                              |

Now we finished editing our FSM, the final result should look like this:

Next, we compile our graphical representation of the state machine into synthesizable VHDL.

|                           | OL.D | A - StateCAD(r)                     |                |  |  |  |

|---------------------------|------|-------------------------------------|----------------|--|--|--|

| <u>F</u> ile <u>E</u> dit | ⊻iew | Options Window Help                 |                |  |  |  |

|                           | _    | Compile (Generate HDL) F7           |                |  |  |  |

|                           |      | 3 StateBench (Create Test Bench) F5 | e StateBench P |  |  |  |

| Open File                 | Save | Optimization Wizard                 |                |  |  |  |

|                           |      | Configuration                       |                |  |  |  |

| <b>LL</b>                 |      | Machine <u>Attribute</u>            |                |  |  |  |

There are several options, how our statemachine can be translated to VHDL. The most important option is, whether the outputs are registered or not. We chose not to register our outputs.

| Optimize Outputs for Speed                                                                                                                                                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Select outputs to be made reg                                                                                                                                                                                                         |

| X en                                                                                                                                                                                                                                  |

| Disable Optimize Speed                                                                                                                                                                                                                |

| Optimize Cancel Help                                                                                                                                                                                                                  |

| Output signals which can be made<br>registered are listed here. Select the<br>signals to make into registered (X<br>before the names), or disable this<br>optimization. This feature may be<br>enabled from the Configuration dialog. |

The parser detected, that there is no transition leaving the stop state, except for a reset condi-

tion. For our machine this is intentional, so we may safely ignore this warning.

| View Warnings                                                                    | ×                    |

|----------------------------------------------------------------------------------|----------------------|

| ID Number: 1 Warning [1]<br>Problem:                                             | Close                |

| Warning[Z125]: Possible stuck at state 'stop'. `<br>exit the state is via reset. | The only way to 🔺    |

| Solution:                                                                        |                      |

| Add a transition (with a non-false condition) awa                                | ay from the state. 📥 |

| ]                                                                                | 7                    |

| Help: Click here for additional info                                             | rmation.             |

|                                                                                  |                      |

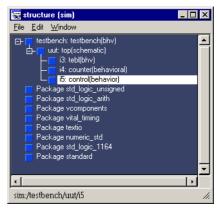

Finally, the generated source code is displayed for review. You should have a look at the code and check, if this reflects, what you had in mind.

| StateCAD HDL Browser - c:\mydocs\tt\part2\CONTROL.vhd             |

|-------------------------------------------------------------------|

| File <u>V</u> iew                                                 |

| LIBRARY ieee;                                                     |

| USE ieee.std_logic_1164.all;                                      |

| ENTITY CONTROL IS                                                 |

| PORT (CLK,pbrun,pbstop,RESET: IN std_logic;                       |

| en : OUT std_logic);                                              |

| END;                                                              |

| ARCHITECTURE BEHAVIOR OF CONTROL IS                               |

| <ul> <li>State variables for machine sreg</li> </ul>              |

| SIGNAL idle, next_idle, run, next_run, stop, next_stop : std_logi |

| SIGNAL next_en : std_logic;                                       |

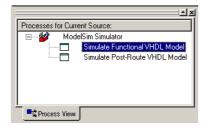

We exit the FSM Editor now and find ourselves back in the Project Navigator. Unfortunately our statemachine has not been added to project, so we need to do this manually.

| Xilinx - Project Navigator - c:\myDocs\tt\part2\part2.npl |              |         |             |                   |         |               |                |              |   |   |    |

|-----------------------------------------------------------|--------------|---------|-------------|-------------------|---------|---------------|----------------|--------------|---|---|----|

| <u>F</u> ile                                              | <u>E</u> dit | ⊻iew    | Project     | <u>S</u> ource    | Process | <u>M</u> acro | <u>W</u> indow | <u>H</u> elp |   |   |    |

|                                                           |              |         | <u>N</u> ew | Source            |         |               |                | <b>a</b> R:  | . | 9 | N? |

|                                                           | _            |         | Add         | Source            |         | Inse          | rt             | - V4         |   | • |    |

|                                                           |              |         | Add         | <u>C</u> opy of S | ource   | Shif          | t+Insert       |              | _ | _ | _  |

| So                                                        | urces i      | n Proie |             |                   |         |               |                |              |   |   |    |

For convenience, we add both, the VHDL file, and its graphical representation to our project. This allows us to open the diagram later on by simply double clicking the *.dia* file. Unlike the *.vhd* file, the *.dia* file is *not* required for synthesis.

| Add Existing        | Sources                                             |       | ? ×             |

|---------------------|-----------------------------------------------------|-------|-----------------|

| <u>S</u> uchen in:  | 🔁 part2 💌                                           | 🗕 🖻 🖻 | * <b>III</b> •  |

| Compile             | 🔊 te-bl.vhd                                         |       |                 |

| sic                 |                                                     |       |                 |

| work                |                                                     |       |                 |

| CONTRO              |                                                     |       |                 |

|                     |                                                     |       |                 |

| 🖹 counter.vi        | na                                                  |       |                 |

|                     |                                                     |       |                 |

|                     |                                                     | r     |                 |

| Datei <u>n</u> ame: | "CONTROL.vhd" "CONTROL.DIA"                         |       | Ö <u>f</u> fnen |

| Dateityp:           | Sources (*.txt;*.sch;*.vhd;*.vhd;*.vhd;*.vhd;*.dia  | 1 -   | Abbrechen       |

| <u>-</u>            | Teeneer ( and ready initial initial initial initial |       | /               |

Again, we are asked for the type of our VHDL source.

| Choose Source Type                                                       | ×            |

|--------------------------------------------------------------------------|--------------|

| control.vhd is which source type?<br>The suffix is ambiguous as to type. |              |

| VHDL Module<br>VHDL Package<br>VHDL Test Bench                           | OK<br>Cancel |

|                                                                          |              |

To create a schematic symbol for our state machine, we select the source file.

| Sources in Project:          |

|------------------------------|

| 🖃 🖻 Untitled                 |

| 🛄 💼 control.dia              |

| 🖻 📲 2S200 PQ208-5 - XST VHDL |

| - V control (control.vhd)    |

| counter (counter.vhd)        |

| Tel: Module                  |

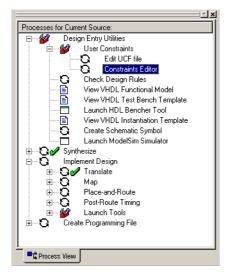

Double clicking *Create Schematic Symbol* creates the symbol, which is indicated by the green check mark.

| Processes for Current Source:                                            |

|--------------------------------------------------------------------------|

| 🕞 🗝 🌌 🛛 Design Entry Utilities                                           |

| 😟 🕀 🚽 User Constraints                                                   |

| 📄 🛛 📄 View VHDL Test Bench Template                                      |

| Launch HDL Bencher Tool                                                  |

| 📄 🛛 View VHDL Instantiation Template                                     |

| 🖳 🔂 🖌 Create Schematic Symbol                                            |

| Launch ModelSim Simulator                                                |

| Emmin Synthesize<br>Emmin Synthesize<br>Implement Design                 |

| I⊞CI Synthesize<br>I⊞CQ Implement Design<br>I≣CQ Create Programming File |

| 🗄 💮 Create Programming File                                              |

|                                                                          |

| Process View                                                             |

Creating state machines is a non-trivial task. It is highly recommended to get familiar with the various options of the state machine editor, their effect on the generated VHDL code and their effect on synthesis and implementation.

### **Using the Schematic Editor**

The top layer of our design is created with the schematic editor, instantiating the symbols being defined during previous design entry steps. First, we need to create a new source.

| Xilinx - Project Navigator - c:\myDocs\tt\part2\part2.npl |                    |                |            |               |                |              |     |

|-----------------------------------------------------------|--------------------|----------------|------------|---------------|----------------|--------------|-----|

| <u>F</u> ile <u>E</u> dit ⊻iew                            | Project            | <u>S</u> ource | Process    | <u>M</u> acro | <u>W</u> indow | <u>H</u> elp |     |

| □ 🚅 🗔 🕻                                                   | New Source         |                |            |               |                | <b>N</b> 64  | 🤋 💦 |

|                                                           | Add Source         |                | Insert     |               |                | • •          |     |

|                                                           | Add Copy of Source |                |            | Shif          | t+Insert       |              |     |

| Sources in Proje                                          | Dele               | te Implem      | entation D | ata           |                |              |     |

We specify *Schematic* as the source type and enter file name and location.

| New                                                                                                           | ×                                                                   |

|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| User Document<br>Schematic<br>VHDL Module<br>VHDL Package<br>VHDL Test Bench<br>Vhdl Library<br>State Diagram | File Name:         top         Logation:         c:\mydocs\tt\part2 |

| < Zuriick We                                                                                                  | eiter >AbbrechenHilfe                                               |

A summary is displayed, before actually creating the new source.

|        | w skeleton sourc                      | e with the        |        |

|--------|---------------------------------------|-------------------|--------|

| ematic |                                       |                   |        |

|        |                                       |                   |        |

|        |                                       |                   |        |

|        |                                       |                   |        |

|        |                                       |                   |        |

|        |                                       |                   |        |

|        |                                       |                   |        |

|        | will create a ne<br>ations:<br>ematic | ations:<br>ematic | ematic |

Then, the schematic editor is launched, displaying an empty sheet.

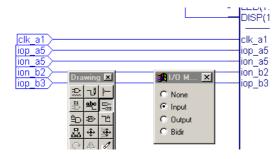

First, we add our previously created schematic symbols to the sheet.

| 🔡 S          | chem         | atic E | ditor -           | top - She       | et 1          |             |         |              |        |

|--------------|--------------|--------|-------------------|-----------------|---------------|-------------|---------|--------------|--------|

| <u>F</u> ile | <u>E</u> dit | ⊻iew   | Add               | Template        | <u>T</u> ools | <u>D</u> RC | Options | <u>H</u> elp |        |

| DI           | 2   E        | ] 8    | <u>v</u>          | <u>/</u> ire    |               | F3          | ДΙГ     |              | æ∄ ⊉ 1 |

|              |              |        | <u>N</u>          | et Name         |               | F4          |         |              |        |

|              |              |        | Expanded Bus Name |                 |               |             |         |              |        |

|              |              |        | <u>B</u>          | us Tap          |               |             |         |              |        |

|              |              |        | 12                | <u>0</u> Marker |               | Alt+M       |         |              |        |

|              |              |        | Symbol            |                 |               | F2          |         |              |        |

|              |              |        | <u>l</u> r        | nstance Nari    | ne            |             |         |              |        |

|              |              |        |                   |                 |               |             | _       |              |        |

The library window pops up. We add the symbols *control, counter* and *tebl* to the sheet.

| Schematic Editor - top - Sheet 1              |                       |

|-----------------------------------------------|-----------------------|

| Elle Edit View Add Template Tools DRC Options | Help                  |

| DISH & MAR 2 PPB D                            | 기미미 34월 11 / 9        |

|                                               | Symbol Libraries      |

|                                               |                       |

| L. CONTROL                                    | Libraries/Directories |

| - COL                                         | (All Symbols)         |

| there a -                                     | (Local Symbols)       |

|                                               |                       |

|                                               |                       |

|                                               |                       |

|                                               |                       |

| 2 -                                           |                       |

|                                               |                       |

|                                               | Symbols               |

| Drawing X                                     | sonto                 |

| 2 11-                                         | counter               |

| 은 <b>반</b> 52                                 | tebl                  |

| 20 80 TE                                      |                       |

| 品中步                                           |                       |

| C 4 0                                         |                       |

|                                               |                       |

| ALL                                           |                       |

|                                               | 1                     |

|                                               | Symbol Name Filter    |

| <u>.</u>                                      |                       |

| Symbol - Click to Place Symbol 'CONTROL'      |                       |

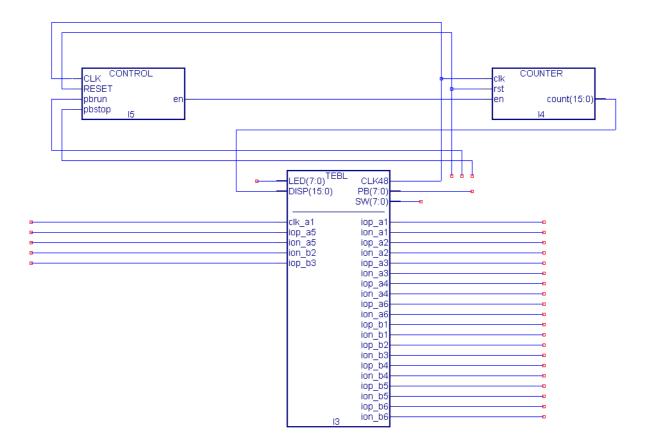

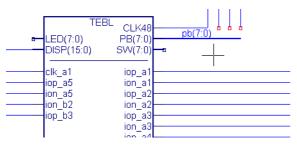

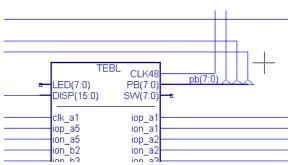

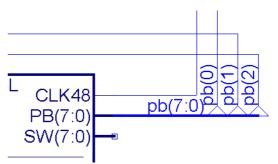

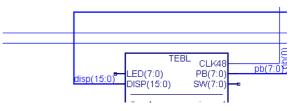

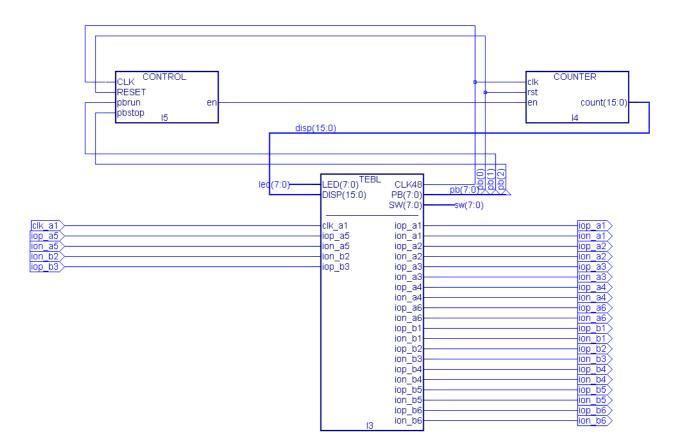

After adding the symbols, our sheet looks like this.

| Schematic Editor - top - Sheet 1                   |                                                             |

|----------------------------------------------------|-------------------------------------------------------------|

| Elle Edit View Add Template Tools DRC Options Help |                                                             |

|                                                    | 31월 11 V 🔋                                                  |

|                                                    |                                                             |

| Symbol - Click to Place Symbol 'TEBL'              | Sumbole<br>Control<br>Counter<br>125<br>Symbol Liame Filter |

Probably, we need to tidy up our symbols a bit.

| 22 S | chematic Edito                                                       | r - TOP - SI                  | neet 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------|----------------------------------------------------------------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | <u>E</u> dit <u>V</u> iew <u>A</u> o<br><u>U</u> ndo<br><u>R</u> edo | ld Template<br>F9<br>Shift+F9 | Iools DRC Options Help<br>으 우ር 다음을 생활 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|      | Cu <u>t</u><br>Copy<br>Copy Image<br><u>P</u> aste                   | Ctrl+X<br>Ctrl+C<br>Ctrl+V    | =-cik <sup>CO</sup><br>=-ak<br>=-ak                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | <u>D</u> elete<br>Dup <u>l</u> icate                                 | F5<br>F6                      | TEBL CLX48-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      | <u>M</u> ove<br>Drag<br>R <u>o</u> tate<br>Mjrror                    | F7<br>F8<br>Ctrl+R<br>Ctrl+E  | - LECTON PETOD<br>- DEST(55) SW(75)<br>- CRL<br>- CR |

|      | <u>A</u> ttribute<br>Tabl <u>e</u> Data                              | •                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|      | Sym <u>b</u> ol                                                      |                               | 100_02-40<br>100_03-44<br>100_044-40<br>100_044-40<br>100_044-40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

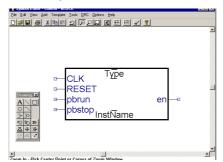

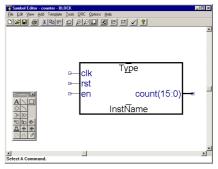

Clicking on symbol will open the symbol editor window. We adjust *control* to look like this.

And exit the symbol editor.

| 📸 Symbol Editor                        | Symbol Editor - control - BLOCK |    |     |     |   |     |    |    |   |    |       |    |            |            |    |   |     |   |   |   |

|----------------------------------------|---------------------------------|----|-----|-----|---|-----|----|----|---|----|-------|----|------------|------------|----|---|-----|---|---|---|

| <u>F</u> ile <u>E</u> dit <u>V</u> iew | Add                             | Te | mpļ | ate | ] | ool | s  | DF | С | Op | otior | ns | <u>H</u> e | lp         |    |   |     |   |   |   |

| <u>N</u> ew<br>Open                    |                                 |    | 1   | B   |   | 2   | Γ. | €  | ۶ |    | ]     | ľ  | 2          | <b>8</b> 7 | ÷. | E | IJ. | ~ | 1 | 9 |

|                                        | Ctrl+S                          |    | ÷   | Ì   | : | Ì   | :  | Ì  | : |    |       | :  |            | :          | Ì  | : | Ì   | : |   | : |

| Save <u>A</u> s                        |                                 |    |     |     |   |     |    |    |   | ·  |       |    |            |            |    |   |     |   |   |   |

| Page Set <u>u</u> p<br>Print           |                                 |    | ľ   | ÷   | : | ÷   |    |    |   |    | ÷     |    | •          |            | ÷  | : | ÷   | : |   |   |

| Print Image                            |                                 |    | ŀ   | ÷   | • | ÷   | •  | ·  |   | ·  |       | ·  | •          | ·          | ·  |   | ·   |   | · | • |

| Exit                                   |                                 |    | Ľ   |     |   |     |    |    |   |    |       |    |            |            |    |   |     |   |   |   |

|                                        |                                 |    | Ē   |     | - |     |    |    |   |    | _     |    |            |            |    |   |     |   | _ | _ |

The schematic editor notifies us before updating the symbols. We click *OK TO ALL*.

| Schematic Editor |                                                                                                                                                                |           |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--|--|--|--|--|

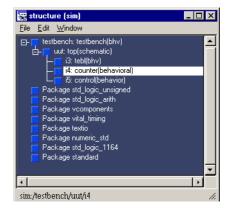

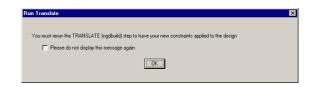

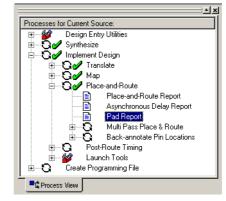

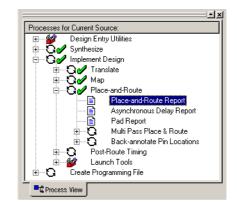

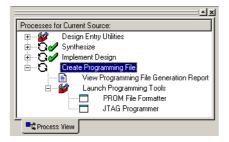

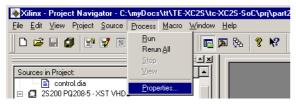

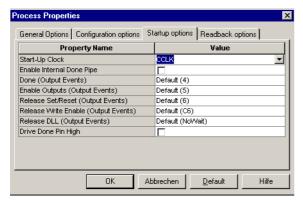

| ⚠                | References to symbol control are out of date.<br>When you close this schematic, you will be asked if<br>you want to save it, even if you have made no changes. |           |  |  |  |  |  |